## Обзор архитектуры межсоединений ПЛИС на примере производителей XILINX и ALTERA

К.В. Зольников $^1$ , В.А.Попов $^1$ ,  $^1$ ФГБОУ ВО «Воронежский государственный лесотехнический университет имени Г.Ф. Морозова»

<sup>2</sup>АО «Интеллектуальные микросистемы»

В работе рассматриваются программируемые логические интегральные схемы (ПЛИС) ведущих производителей Xilinx и Altera. Проводится анализ трассировочной матрицы - одного из важнейших структурных элементов любой ПЛИС. По результатам анализа установлено, что Cyclone 4 обеспечивает более высокую плотность интеграции блоков и быстрый доступ к данным. Spartan 6 более гибкая и удобная в использовании ПЛИС.

Ключевые слова: ПЛИС, трассировка, межсоединения, блоки коммутации, Xilinx, Altera.

Программируемые логические интегральные схемы (ПЛИС) являются одним из самых важных элементов в современных системах электроники. Они используются в автомобильной электронике, медицинской технике, телекоммуникации и многих других. ПЛИС предоставляют возможность быстрого проектирования и реализации сложных электронных систем, что делает их очень популярными среди разработчиков электронной и радиоаппаратуры. [1-3]

В настоящее время как никогда ранее возросла необходимость разработки отечественных ПЛИС. В современных условиях уже нельзя ограничиваться простым созданием аналогов зарубежных схем, требуется разработка абсолютно новых ПЛИС с новой архитектурой. Анализ архитектуры ПЛИС ведущих производителей позволит приблизить инженеров к решению этой проблемы.

Современные ПЛИС ведущих производителей включают в себя блоки выполняющие одинаковые функции, однако могут иметь разную структуру. Основные структурные элементы любых ПЛИС: І/О — элементы, ячейки конфигурационной памяти, логические элементы, блоки пользовательской памяти, блоки цифровой обработки сигналов, а также трассировочная матрица. Трассировочная матрица любой ПЛИС представляет собой сложную «сеть» коммутаторов и проводников, благодаря которой осуществляется связь между ключевыми элементами ПЛИС, перечисленными выше. В данной статье мы

рассмотрим отличия в трассировочной матрице ПЛИС двух ведущих производителей Xilinx и Altera. [4-8]

## Архитектура межсоединений, используемая в ПЛИС фирмы Xilinx

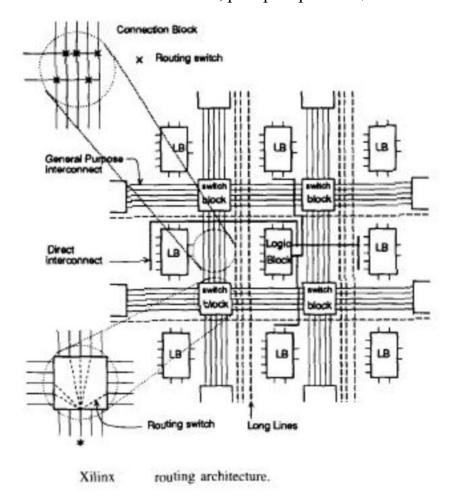

В архитектуре межсоединений Xilinx существует четыре основных типа трассировочных сегментов, представленных на рисунке 1 [9]:

- General purpose interconnect сегменты общего назначения, которые проходят через переключатели в коммутационные блоки (routing switch).

- Direct interconnect прямое соединение, коммутирующее выводы логического блока с четырьмя окружающими блоками подключения

- Long line протяженные соединения с высокой разветвленностью и равномерной задержкой

- Clock lines тактовые сигналы, распространяющиеся по всей ПЛИС.

Рисунок 1 – Архитектура межсоединений, используемая в ПЛИС фирмы Xilinx [9]

В схеме маршрутизации Xilinx подключение входов/выходов логического блока к трассировочному каналу выполняется через блок подключения (connection block). Поскольку для реализации матрицы конфигурационной технология SRAM, используется образуются подключений. Логический блок окружен блоками подключения (connection block) с четырех сторон. Они соединяют выводы логического блока с сегментами проводов. Проходные транзисторы используются для реализации подключения выходных выводов логических блоков, в то время как использование мультиплексоров для входных выводов экономит количество ячеек SRAM, необходимых для каждого вывода. Вывода логического блока, подключенные к соединительными блокам (connection block), затем могут быть подключены к любому количеству сегментов проводов через коммутационные блоки (routing switch).

## Методология маршрутизации Altera

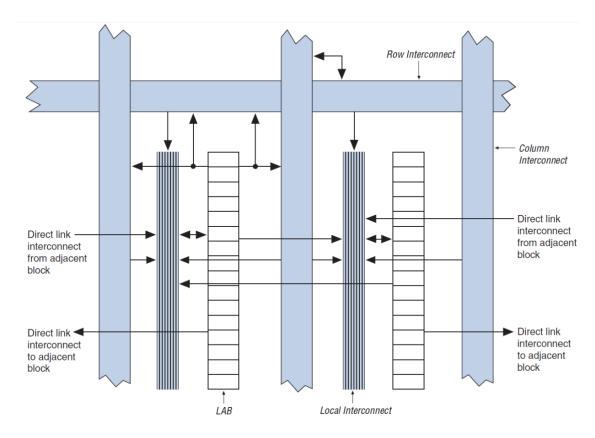

Архитектура маршрутизации Altera имеет двухуровневую иерархию. На первом уровне иерархии, 16 или 32 логических элемента сгруппированы в блок логического массива. Вторым уровнем иерархии являются глобальные вертикальные и горизонтальные шины данных, распространяющиеся на 4, 16 и 24 блока логических массивов. [10]

На рисунке 2 представлены основные типы межсоединений, используемые в ПЛИС Altera:

- direct link interconnect

- local interconnect

- column/row interconnect

- clock networks

Рисунок 2 — Архитектура межсоединений, используемая в ПЛИС фирмы Altera [10]

Логические элементы коммутируются друг с другом с помощью (local interconnect). Коммутация логических локальных межсоединений элементов с соседними блоками (слева/справа) может осуществляться через прямые соединения (direct link interconnect). К локальным межсоединениям подключаются вертикальные (column interconnect) И горизонтальные межсоединения (row interconnect), посредством которых осуществляется взаимодействие с отдаленными блоками, такими как блоки пользовательской памяти, цифровой обработки сигналов и т.д. Коммутаторы, осуществляющие соединение локальных и глобальных трассировочных ресурсов, располагаются по обеим сторонам (слева и справа) от функциональных блоков. Clock networks – сеть тактовых сигналов (отсутствует на рисунке 2) обеспечивает эффективное распространение управляющих сигналов, таких как тактовый сигнал, сигналы сброса и предустановки и т.д.

Исследования показывают, что блоки памяти в ряде ПЛИС производства Altera обеспечивают более быстрый доступ к данным, чем в производства Xilinx [11, 12]. Однако, как отмечается в статье "Comparison of FPGA Architectures",

опубликованной в журнале "International Journal of Engineering Research and Applications", архитектура межсоединений например в Spartan 6 производства Xilinx более гибкая и удобная в использовании, чем в Cyclone 4 производства Altera. Это означает, что проектирование электронных систем с помощью Spartan 6 может быть более простым и быстрым, чем с помощью Cyclone 4.

В целом, выбор между Cyclone 4 и Spartan 6 зависит от конкретных требований приложения. Если необходима высокая плотность интеграции блоков и быстрый доступ к данным, то, к примеру, Cyclone 4 может быть лучшим выбором. Если же необходима гибкость и удобство в использовании, то Spartan 6 может быть предпочтительнее. Кроме того, стоит учитывать затраты на разработку и производство электронных систем на основе каждой ПЛИС.

В заключение, архитектуры межсоединений в Cyclone 4 и Spartan 6 имеют свои преимущества и недостатки, и выбор между ними зависит от конкретных требований приложения. Cyclone 4 обеспечивает более высокую плотность интеграции блоков и быстрый доступ к данным, что делает ее подходящей для приложений, требующих высокой скорости обработки данных. С другой стороны, Spartan 6 более гибкая и удобная в использовании, что может быть предпочтительнее для проектирования сложных электронных систем. Кроме того, стоит учитывать затраты на разработку и производство электронных систем на основе каждой ПЛИС. В итоге, выбор между Cyclone 4 и Spartan 6 должен основываться на анализе конкретных требований приложения и возможностей каждой ПЛИС.

## Литература

- 1. Макаренко Ф.В., Ягодкин А.С., Зольников К.В., Денисова О.А., Полуэктов А.В. Обзор логических базисов и микросхем при построении комбинационного устройства с учетом надежности// Моделирование систем и процессов. 2022. Т. 15, № 1. С. 115-124.

- 2. Суханов, В.В. Логическое проектирование информационного обеспечения распределенных информационных систем критического применения / В.В. Суханов, О.В. Ланкин // Моделирование систем и процессов. 2021. Т. 14, № 2. С. 67-73. DOI: 10.12737/2219-0767-2021-14-2-67-73.

- 3. Суханов, В.В. Методика логического проектирования информационного обеспечения распределенных информационных систем критического

- применения / В.В. Суханов, О.В. Ланкин // Моделирование систем и процессов. 2021. Т. 14, № 3. С. 67-73. DOI: 10.12737/2219-0767-2021-14-3-67-73.

- 4. Кроткова Н. А. Программируемые логические интегральные схемы (ПЛИС) //Научный альманах. -2020. №. 9-2. C. 37-39.

- 5. Наваби 3. Проектирование встраиваемых систем на ПЛИС: ДМК Пресс. Москва, 2016. 464 с. ISBN 978-5-97060-174-7

- 6. Ушенина И. В. Современные направления развития ПЛИС архитектуры FPGA //XXI век: итоги прошлого и проблемы настоящего плюс. 2017. №. 4. С. 120-124.

- 7. Гаврилов С. В., Железников Д. А., Хватов В. М. Решение задач трассировки межсоединений с ресинтезом для реконфигурируемых систем на кристалле //Известия высших учебных заведений. Электроника. 2017. Т. 22. N2. C. 266-275.

- 8. Строгонов А. В. и др. Архитектура ПЛИС типа ППВМ с одноуровневой структурой межсоединений //Вестник Воронежского государственного технического университета. 2011. T. 7. №. 3. C. 13-16.

- 9. xilinx.com. Официальный сайт Xilinx. AMD. URL: <a href="https://www.xilinx.com/products/silicon-devices/fpga/spartan-6.html#documentation">https://www.xilinx.com/products/silicon-devices/fpga/spartan-6.html#documentation</a>.

- 10. Corperation A. Cyclone IV FPGA Device Family Overview //Cyclone IV Device Handbook. 2013. T. 1.

- 11. Murray K. E. et al. Vtr 8: High-performance cad and customizable fpga architecture modelling //ACM Transactions on Reconfigurable Technology and Systems (TRETS).  $-2020. -T. 13. N_{\odot}. 2. -C. 1-55$ .

- 12. Nguyen T. et al. The performance and energy efficiency potential of FPGAs in scientific computing //2020 IEEE/ACM Performance Modeling, Benchmarking and Simulation of High Performance Computer Systems (PMBS). IEEE, 2020. C. 8-19.